| PART NO.:   |  |

|-------------|--|

| FOR MESSRS: |  |

# CONTENTS

| NO. | ITEM                                      | PAGE    |

|-----|-------------------------------------------|---------|

| 1,  | COVER                                     | 1       |

| 2.  | RECORD OF REVISION                        | 2       |

| 3.  | GENERAL SPECIFICATION AND MECHANICAL DATA | 3       |

| 4.  | ABSOLUTE MAXIMUM RATINGS                  | 4       |

| 5.  | ELECTRICAL CHARACTERISTICS                | 5       |

| 6.  | OPTICAL CHARACTERISTICS                   | 6       |

| 7.  | BLOCK DIAGRAM                             | 7       |

| 8.  | TIMING CHARACTERISTICS                    | 8       |

| 9.  | DIMENSIONAL OUTLINE                       | 9~11    |

| 10. | FUNCTIONAL DESCRIPTION                    | 12 ~ 20 |

| Accepted by: | Proposed by: | Jack | (fon | 1/05 |

|--------------|--------------|------|------|------|

| 2            |              |      |      | 195  |

# RECORD OF REVISION

| DATE     | PAGE    | SUMMARY .                                                                                                                                                                                                                                                                                           |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-10-'96 | 3<br>7  | 1) 3.3(2) MODULE SIZE: 35.7H → 34.7H<br>2) ICOM CONTROL LINE: Y20 → Y21.Y37 → Y32.<br>Y38 → Y33.Y55 → Y58.Y69 → Y70.Y82 → Y<br>79.                                                                                                                                                                  |

|          | 9<br>10 | 3) PCB HEIGHT: 35.7 → 34.7mm<br>4) PIN NO. 3: RES → LEDB.L                                                                                                                                                                                                                                          |

| 7-05-'96 | 3       | <ol> <li>MODULE SIZE: 6.8D → 7.3D</li> <li>3.3(3)EFFECTIVE AREA: 44.5W → 43.7W         26.6W → 25.7H</li> <li>3.3(4) ACTIVE AREA: 39.96W → 38.97W,         21.56H → 20.13H.</li> <li>DOT SIZE: 0.41H → 0.39H,</li> <li>DOT PITCH: 0.40W → 0.39W, 0.45H → 0.42H.</li> <li>LCD TYPE: G → Y</li> </ol> |

|          | 4       | 7) 4.2 SHOCK: OPERATING 3G max → 10G max. STORAGE 50G max → 100G max.                                                                                                                                                                                                                               |

|          |         |                                                                                                                                                                                                                                                                                                     |

|          |         | ·                                                                                                                                                                                                                                                                                                   |

|          |         |                                                                                                                                                                                                                                                                                                     |

|          |         |                                                                                                                                                                                                                                                                                                     |

|          |         |                                                                                                                                                                                                                                                                                                     |

|          |         |                                                                                                                                                                                                                                                                                                     |

#### 3. GENERAL SPECIFICATIONS AND MECHANICAL DATA

3.1 GENERAL SPECIFICATIONS

PLEASE REFER TO:

"CUSTOMER ACCEPTANCE STANDARD SPECIFICATIONS (MS-10-10000)".

- 3.2 THIS INDIVIDUAL SPECIFICATION IS PRIOR TO GENERAL SPECIFICATIONS.

- 3.3 MECHANICAL DATA

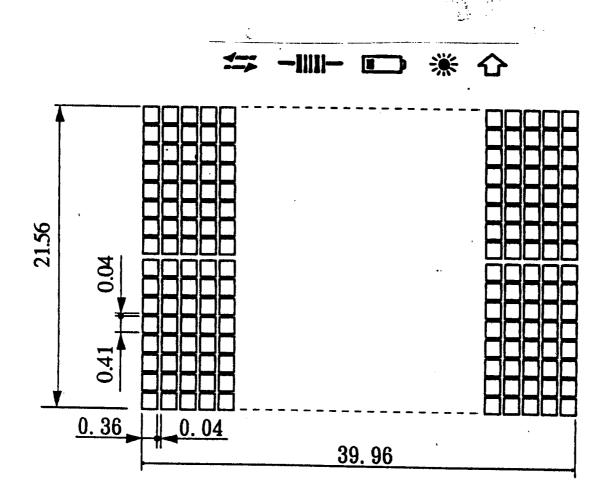

| (1) | NUMBER | OF | DOTS |  | 100W | * | 48H | <b>DOTS</b> |  |

|-----|--------|----|------|--|------|---|-----|-------------|--|

|-----|--------|----|------|--|------|---|-----|-------------|--|

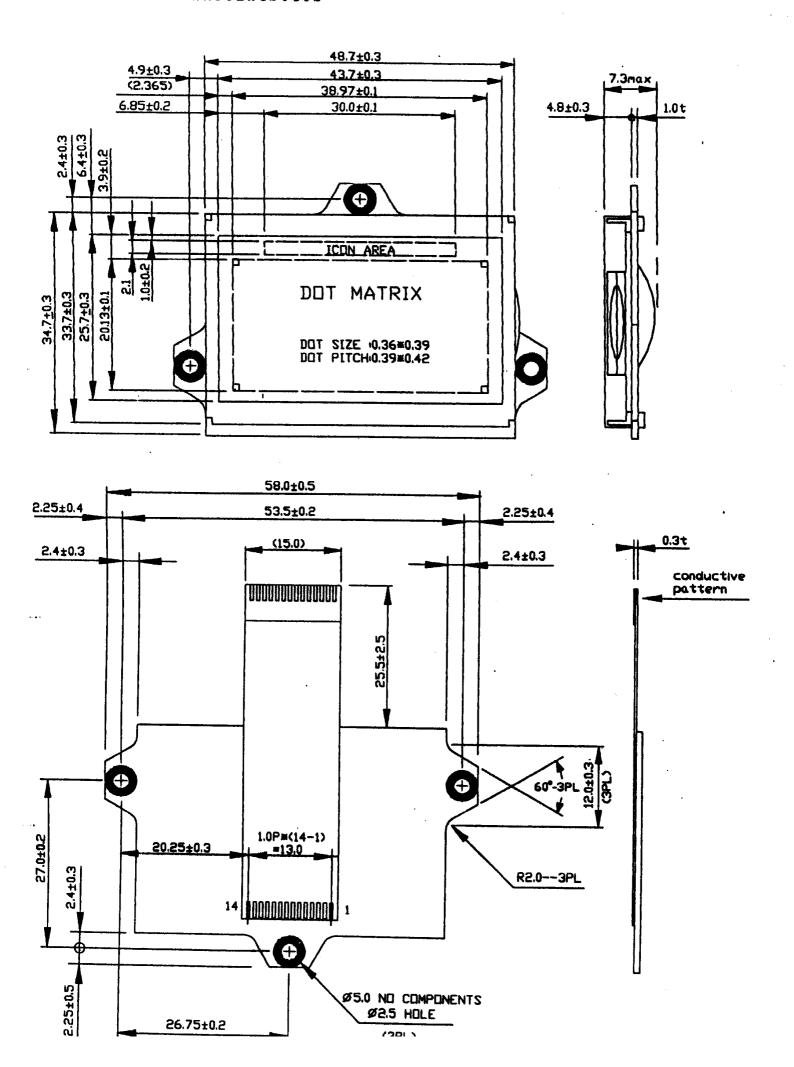

(2) MODULE SIZE ----- 48.7W \* 34.7H \* 7.3D (max) mm

(3) EFFECTIVE AREA ----- 43.7W \* 25.7H mm

(4) ACTIVE AREA ----- 38.97W \* 20.13H mm

(5) DOT SIZE ----- 0.36W \* 0.39H mm

(6) DOT PITCH ----- 0.39W \* 0.42H mm

(7) VIEWING DIRECTION ---- 6 O'CLOCK

(8) LCD TYPE ----- STN.YELLOW.TRANSFLECTIVE.

(9) LED COLOR ----- YELLOW-GREEN

#### 4. ABSOLUTE MAXIMUN RATINGS

#### 4.1 ELECTRICAL ABSOLUTE MAXIMUM RATINGS.

| ITEM                   | SYMBOL  | MIN. | MAX. | UNIT | COMMENT  |

|------------------------|---------|------|------|------|----------|

| POWER SUPPLY FOR LOGIC | VDD-VSS | 0    | 7.0  | V    |          |

| INPUT VOLTAGE          | ΛΙ      | VSS  | VDD  | V    |          |

| STATIC ELECTRICITY     |         | _    | 100  | V    | NOTE (1) |

| POWER SUPPLUY FOR LED  | VLED    |      | 6.0  | V    |          |

NOTE (1): TEST METHOD AND CONDITIONS AFTER CCHARGING UP 200 PF CAPACITOR BY STATED VOLTAGE. THE CAPACITOR IS CONNECTED WITH INTERFACE PINS OF THE MODULE.

### 4.2 ENVIRONMENTAL ABSOLUTE MAXIMUM RATINGS.

| ITEM                | OPERA   | ATING           | ST      | ORAGE                   |                                             |  |  |

|---------------------|---------|-----------------|---------|-------------------------|---------------------------------------------|--|--|

| 1 1 C ,M            | MIN.    | MAX.            | MIN.    | MAX.                    | COMMENT                                     |  |  |

| AMBIENT TEMPERATURE | -20℃    | 70℃             | -30℃    | 80°C                    | NOTE (2)                                    |  |  |

| HUMIDITY            | NOTE    | TE (3) NOTE (3) |         | WITHOUT<br>CONDENSATION |                                             |  |  |

| VIBRATION NOTE (4)  |         | 0.5G            | <u></u> | 26                      | 10~300HZ<br>XYZ<br>DIRECTIONS<br>1 Hr EACH  |  |  |

| SHOCK<br>NOTE (4)   |         | 10G             |         | 100G                    | 10 mSEC<br>XYZ<br>DIRECTIONS<br>1 TIME EACH |  |  |

| CORROSIVE GAS       | NOT ACC | CEPTABLE        | NOT AC  | CEPTABLE                |                                             |  |  |

NOTE (2) : Ta AT -30℃ : 48HR MAX.

80℃ :168HR MAX.

NOTE (3) : Ta ≤ 60°C : 85% RH MAX.

Ta > 60℃ : ABSOLUTE HUMIDITY MUST BE LOWER THAN THE

HUMIDITY OF 85% RH AT 50℃. (50% RH AT 70℃)

NOTE (4): 1G = 9.8 m/

### 5. ELECTRICAL CHARACTERISTICS.

| ITEM                                   | SYMBOL  | CONDITION    | MIN. | TYP. | MAX. | UNIT |

|----------------------------------------|---------|--------------|------|------|------|------|

| POWER SUPPLY<br>VOLTAGE FOR<br>CIRCUIT | VDD-VSS |              | 4.75 | 5.0  | 5.25 | V    |

| INPUT VOLTAGE                          | VIH     | H LEVEL      | 2.0  |      | VDD  | V    |

| NOTE (2)                               | VIL     | L LEVEL      | 0    | ·    | 0.8  | V    |

| OUTPUT VOLTAGE                         | VOH     | IOH = -0.3mA | 2.4  |      | -    | V    |

| NOTE (1)                               | VOL     | IOL = 3.0mA  |      |      | 0.4  | V    |

| POWER SUPPLY<br>CURRENT<br>NOTE (3)    | IDD     | VDD-VSS=5.0V |      | 3.0  | 5.0  | mA   |

| LCD DISPLAY<br>DUTY RATIO              | DUTY    |              |      | 1/65 |      |      |

| POWER SUPPLY<br>CURRENT<br>FOR LED     | ILED    | VLED(+)=5.0V |      | 40   | 45   | mA - |

NOTE (1) : APPLIED TO TERMINALS DO  $\sim$  D7

NOTE (2) : APPLIED TO TERMINALS E .AO . DO  $\sim$  D7 . R/W

NOTE (3): THE DISPLAY PATTERN IS ALL "ON", OR ALL "OFF"

NOTE (4): RECOMMENDED LCD DIRVING VOLTGE MAY FLUCTUATE ABOUT

= 0.5V BY EACH MODULE.

### 6. OPTICAL CHARACTERISTICS

$Ta = 25^{\circ}C$

| ITEM                                  | SYMBOL            | CONDITION                                                                            | MIN. | TYP. | MAX. | UNIT  | NOTE |

|---------------------------------------|-------------------|--------------------------------------------------------------------------------------|------|------|------|-------|------|

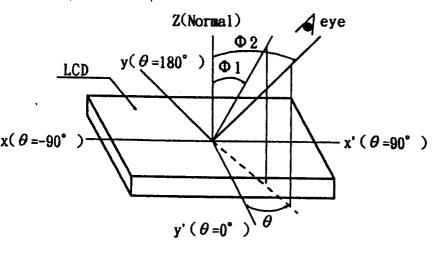

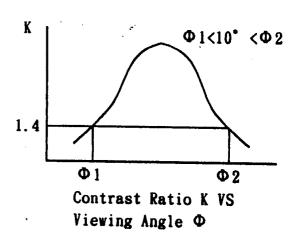

| VIEWING AREA                          | $\Phi 2 - \Phi 1$ | K = 1.4                                                                              | 30   | 40   |      | deg.  | 1~3  |

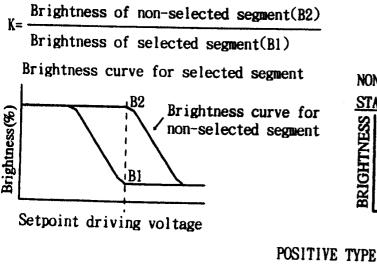

| CONTRAST RATIO                        | K                 | $ \Phi = 10^{\circ} \\ \theta = 0^{\circ} $                                          | 3. 0 | 5. 0 |      |       | 1~3  |

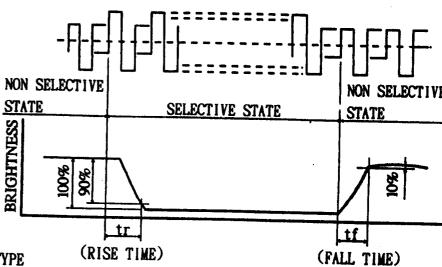

| RESPONSE TIME                         | tr(rise)          | $ \Phi = 10^{\circ} \\ \theta = 0^{\circ} $                                          |      | 250  |      | ms    | 1, 4 |

| RESTORGE TIME                         | tf(fall)          | $ \Phi = 10^{\circ} \\ \theta = 0^{\circ} $                                          |      | 350  |      | ns    | 1, 4 |

| THE BRIGHTNESS OF BACKLIGHTING SOURCE | В                 | $ \begin{array}{ccc} ( * ) \\ \Phi &= 0^{\circ} \\ \theta &= 0^{\circ} \end{array} $ | 3. 0 |      |      | cd/m² |      |

( \* UNDER NORMAL TEMPERATURE AND HUMIDITY IN A DARK ROOM )

NOTE (1): SEE CUSTOMER ACCEPTANCE STANDARD SPECIFICATION FOR DEFINITION OF OPTICAL CHARACTERISTICS

NOTE 1. DEFINITION OF ANGLE  $\theta$  AND  $\Phi$

NOTE 2. DEFINITION OF VIEWING ANGLE \$\Phi\_1\$ AND \$\Phi\_2\$

NOTE 3. DEFINITION OF CONTRAST "K"

NOTE 4. DEFINITION OF OPTICAL RESPONSE

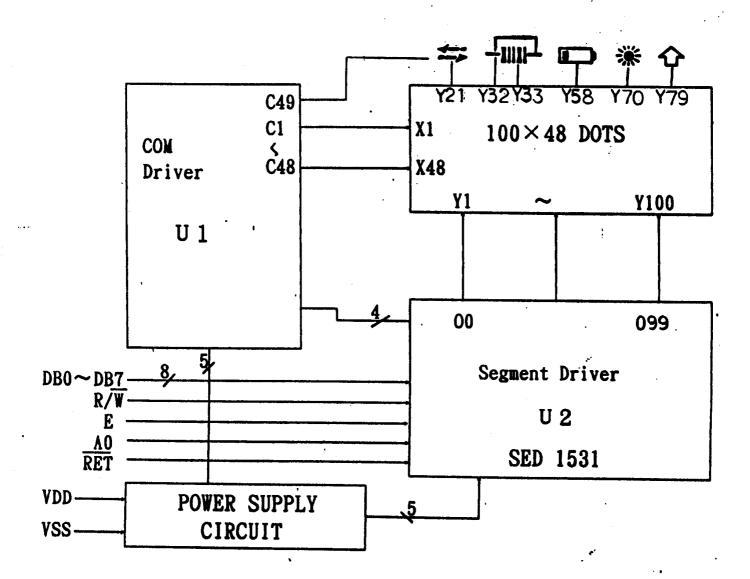

## 7. BLOCK DIAGRAM

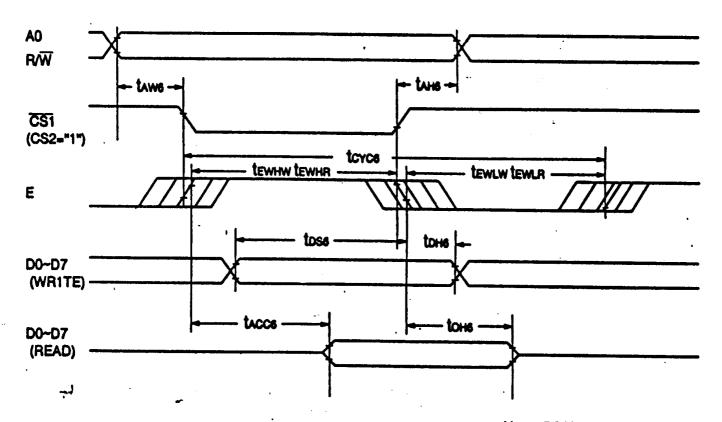

## 6. TINING CHARACTERISTICS

Vpo = 5.0 V ±10%, Ta = -40 to +85°C

| Paramete                                |            | Signal    | Symbol            | Condition | Min.     | Max.     | Unit     |

|-----------------------------------------|------------|-----------|-------------------|-----------|----------|----------|----------|

| System cycle time                       |            |           | tovos             |           | 166      | -        | ns       |

| Address setup time<br>Address hold time | ) <b>e</b> | A0<br>W/Ħ | taws<br>tahs      |           | 10<br>10 |          | ns<br>ns |

| Data setup time<br>Data hold time       |            | D0 to D7  | toss<br>tons      |           | 20<br>10 | •        | ns<br>ns |

| Output disable tim<br>Access time       | 10         | 001007    | tone<br>tacce     | CL=100pF  | 10       | 50<br>70 | ns<br>ns |

| Enable                                  | READ       | E         | t <sub>EWHR</sub> |           | 70       | -        | ns       |

| low pulse width                         | WRITE      | <b>.</b>  | tewnw             |           | 30       | -        | ns ns    |

| Enable                                  | READ       | E         | tewla             | ****      | 70       |          | ns       |

| high pulse width                        | WRITE      | 6         | tewlw             |           | 100      |          | ns       |

### 6. OPTICAL CHARACTERISTICS

### 9.2 INTERFACE

| PIN NO | . SYMBOL | LEVEL | FUNCTION                                                            |

|--------|----------|-------|---------------------------------------------------------------------|

| 1      | VSS      | GND   | GROUND                                                              |

| 2      | VDD      | 5.0V  | POWER SUPPLY FOR LOGIC                                              |

| 3      | IEDB.L   | GND   | GROUND:LED ON                                                       |

| 4      | AO       | L/H   | AO="L" INSTRUCTION REGISTER AO="H" DATA REGISTER                    |

| 5      | R/W      | L/H   | H:DATA READ (LCD MODULE → MPU )<br>L:DATA WRITE (LCD MODULE ← MPU ) |

| 6      | E        | _     | ENABLE SINGAL                                                       |

| 7      | DB7      | . ,-  | DATA INPUT/OUTPUT (MSB)                                             |

| 8      | DB6      | _     | DATA INPUT/OUTPUT                                                   |

| 9      | DB5      |       | DATA INPUT/OUTPUT                                                   |

| 10     | DB4      |       | DATA INPUT/OUTPUT                                                   |

| 11     | DB3      | _     | DATA INPUT/OUTPUT                                                   |

| 12     | DB2      | -     | DATA INPUT/OUTPUT                                                   |

| 13     | DB1      | -     | DATA INPUT/OUTPUT                                                   |

| 14     | DB O     | -     | DATA INPUT/OUTPUT (LSB)                                             |

## 9.3 DETIL DRAWING OF MATERIX PATTERN AND ICOM

| Command                                 |    |    |     |       |      | Code  | ,     |              |                |        |          |                                                                                                                          |

|-----------------------------------------|----|----|-----|-------|------|-------|-------|--------------|----------------|--------|----------|--------------------------------------------------------------------------------------------------------------------------|

|                                         | AO | E  | R∕₩ | D7    | D6   | D5    | D4    | D3           | D2             | D1     | D0       | Function                                                                                                                 |

| (1) Display ON/OFF                      | 0  | 1  | 0   | 1     | 0    | 1     | 0     | 1            | 1              | 1      | 0        | Turns on LCD panel when goes high, and turns off when goes low                                                           |

| (2) Initial Display Line                | 0  | -1 | 0   | 0.    | 1    | Start | displ | ay add       | dress          |        |          | Specifies RAM display line for COM0.                                                                                     |

| (3) Set Page Address                    | 0  | 1  | 0   | 1     | 0    | 1     | 1     | Pag          | e add          | ress   | . •      | Sets the display RAM page in Page Address register.                                                                      |

| (4) Set Column Address<br>4 higher bits | 0  | 1  | 0   | 0     | 0    | 0     | 1     | High<br>addr | er col         | nŵu    |          | Sets 4'higher bits of column address of display RAM in registr                                                           |

| (4) Set Column Address<br>4 lower bits  | 0  | 1  | 0   | 0     | 0    | 0     | 0     | Lowe         | er colu        | ımn    |          | Sets 4 lower bits of column address of display RAM in registe                                                            |

| (5) Read Status                         | 0. | 0  | 1   | Statu | 18   |       |       | 0            | 0              | 0      | 0        | Reads the status information.                                                                                            |

| (6) Write Display Data                  | 1  | 1  | 0   | Write | data |       |       |              | <del></del> -  |        | <u> </u> | Writes data in display RAM.                                                                                              |

| (7) Read Display Data                   | 1  | 0  | 1   | Read  | data |       |       |              |                |        |          | Reads data from display RAM.                                                                                             |

| (8) ADC Select                          | 0  | 1  | 0   | 1     | 0    | 1     | 0     | 0            | 0              | 0      | 0        | Sets normal relationship between RAM column address and segment driver when low, but reverses the relationship when high |

| (9) Normal/Reverse Display              |    | 1  | 0   | 1     | 0    | 1     | 0     | 0            | 1              | 1      | 0        | Normal indication when low, but full indication when high.                                                               |

| (10) Entire Display ON/OFF              | 0  | 1  | 0   | 1     | 0    | 1     | 0     | 0            | 1              | 0      | 0        | Selects normal display (0) or Entire Display ON (1).                                                                     |

| (11) Set LCD Bias                       | 0  | 1  | 0   | 1,    | 0    | 1     | 0     | 0            | 0              | 1      | 0        | Sets LCD drive voltage bias ratio                                                                                        |

| (12) Read-Modify-Write                  | 0  | 1  | 0   | 1     | 1    | 1     | 0     | 0            | 0              | 0      | 0        | Increments Column Address counter during each write when high and during each read when low.                             |

| (13) End                                | 0  | 1  | 0   | 1     | 1.   | 1     | 0     | 1            | 1              | 1      | 0        | Releases the Read-Modify-Write.                                                                                          |

| (14) Reset                              | 0  | 1  | 0   | 1     | 1    | 1     | 0     | 0            | 0              | 1      | 0        | Resets internal functions.                                                                                               |

| (15) Set Power Control                  | 0  | 1  | 0   | 0     | 0    | 1     | 0     | 1            | Oper<br>statu: |        |          | Selects the power circuit operation mode.                                                                                |

| (16) Set Electronic Control<br>Register | 0  | 1  | 0   | 1     | 0    | 0     | Elect | ronic (      | contro         | l valu | •        | Sets V5 output voltage to Electronic Control register.                                                                   |

| (17) Set Standby                        | 0  | 1  | 0   | 1     | 0    | 1     | 0     | 1            | 1              | 0      | 0        | Selects standby status. 0: OFF 1: ON                                                                                     |

| (18) Power Save                         | -  | _  | -   | -     | -    | -     | -     | -            | -              | -      | -        | Compound command of display OFF and entire display ON                                                                    |

#### · Command set

#### (1) Display ON/OFF

Altematively turns the display on and off.

| AO | E | R/W | D7 | D6 | D 5 | D4 | D3 | D2 | D 1 | DO |

|----|---|-----|----|----|-----|----|----|----|-----|----|

| 0  | 1 | 0   | 1  | 0  | 1   | 0  | 1  | 1  | 1   | D  |

The display turns off when D goes low, and it turns on when D goes high.

#### (2) Start Display Line

Specifies line address (refer to Figure 4) to determine the initial display line, or COMO. THE RAM display data becomes the top line of LCD screen. It is followed by the higher number of lines in ascending order, corresponding the the duty cycle. When this commend changes the line address, the smooth screling or page change takes place.

| AO | E | R/W | D7 | D 6 | D 5 | D 4 | D3  | D2 | D1  | DO |

|----|---|-----|----|-----|-----|-----|-----|----|-----|----|

| 0  | 1 | 0   | 0  | 1   | A 5 | A 4 | `A3 | A2 | A 1 | AO |

← High-order bit

| A 5         | A 4 | A 3         | A2  | A1          | AO          | Line address  |

|-------------|-----|-------------|-----|-------------|-------------|---------------|

| 0<br>0<br>0 | 0 0 | 0<br>0<br>0 | 0 0 | 0<br>0<br>1 | 0<br>1<br>0 | 0<br>1<br>2   |

| 1           | 1   | 1           | 1   | 1           | 0<br>1      | :<br>62<br>63 |

#### (3) Set Page Address

Specifies page address to load display RAM data to page ad dress register. Any RAM data bit can be accessed when its page address and column address are specified. The display remains unchanged even when the page adddress is changed. Page address 8 is the display RAM area dedicate to the indicator, and only DO is valid for data change.

| ΑO | E | R/W | D7 | D6 | D 5 | D 4 | D3 | D 2 | D 1 | DO |

|----|---|-----|----|----|-----|-----|----|-----|-----|----|

| 0  | 1 | 0   |    |    |     |     |    |     |     |    |

Relationship between display data RAM and addresses (if initial display line is 1CH):

| Page<br>address                       | Date           | a                                            |        | -        |     | _            |         |    |          | ······································ |      |             |     |             | Line<br>addres | ]        |          |         | •           | COM                     |

|---------------------------------------|----------------|----------------------------------------------|--------|----------|-----|--------------|---------|----|----------|----------------------------------------|------|-------------|-----|-------------|----------------|----------|----------|---------|-------------|-------------------------|

|                                       | D0             | 1                                            |        | -        | 1   |              | Ċ       |    |          |                                        |      |             |     |             | 00<br>01       | -        |          | ١-      | 1           | COM 0                   |

| D3, D2,<br>D1,D0                      | D3             |                                              | 6      |          |     |              |         | -  | 1.       |                                        | Pa   | ge ()       |     |             | 02             | 7        |          |         |             | COM 2<br>COM 3          |

| 0,0,0,0                               | D4<br>D5       |                                              | Ċ      | -        | -   |              | ţ:      | ++ | +-       | ·                                      |      |             |     |             | 04<br>05       | 3        |          |         |             | COM 5                   |

|                                       | D6<br>D7<br>D0 | #                                            | -}<br> |          |     | <u>-</u> -   | <u></u> | ┝  | ·∤·<br>+ | · <del> </del> -                       |      |             |     |             | 06<br>07       | }        |          |         | $\parallel$ | COM 8                   |

|                                       | D1<br>D2       | 7                                            |        |          |     |              |         |    |          |                                        |      |             |     |             | 08<br>09       | 1        |          |         | 11          | COM 8<br>COM 9          |

| 0,0,0,1                               | D3             | 7                                            |        |          |     |              |         |    |          |                                        | Pa   | <b>ge</b> 1 |     |             | OA<br>OB       | 7        |          |         | $\parallel$ | COM10<br>COM11          |

|                                       | D5<br>06       | 3                                            | ١      |          |     |              |         |    |          |                                        |      |             |     |             | 00<br>0E       | ‡        |          |         | V           | COM12<br>COM13<br>COM14 |

|                                       | D7             | }                                            | ╁      | $\vdash$ | Н   | _            | ╁       |    | +        | -                                      |      |             |     |             | 0F             | 7        |          |         |             | COM15<br>COM16          |

|                                       | D1             |                                              |        |          |     |              |         |    | ı        |                                        | _    | _           |     |             | 11             | 7        | ŀ        |         | ۱           | COM17<br>COM18          |

| 0,0,1,0                               | D3             | _                                            |        |          |     |              |         |    | l        |                                        | Pa   | <b>30</b> 5 |     |             | 13<br>14       | 3        |          |         | $\Lambda$   | COM19<br>COM20          |

|                                       | D5<br>D6<br>D7 | ‡                                            |        | ,        |     |              |         |    |          |                                        |      |             |     |             | 15<br>18       | }        |          |         | $\Pi$       | COM21<br>COM22          |

|                                       | D0             | +                                            |        |          | H   | _            | T       | H  | t        |                                        |      |             |     |             | 17             | 1        | 1.       | /64<br> | $\prod$     | COM23<br>COM24          |

| 0,0,1,1                               | D2             | 7.                                           |        |          |     |              |         |    | l        |                                        | Pac  | <b>je</b> 3 |     |             | 19<br>1A<br>1B | ‡        |          |         | П           | COM25<br>COM26          |

| 0,0,1,1                               | D4<br>D5       | 3                                            |        |          |     |              |         |    |          |                                        |      | ,           |     |             | 1C<br>1D       | SI       |          | -       | 1           | COM27<br>COM28<br>COM29 |

|                                       | D8<br>D7       | 1                                            | Ц      |          |     | _            |         |    |          |                                        |      |             |     |             | i€<br>iF       | 7        | <b>'</b> |         |             | COM30<br>COM31          |

|                                       | D0<br>D1       |                                              |        |          |     |              |         |    |          |                                        |      |             |     |             | 20<br>21       | }        |          |         |             | COM32<br>COM33          |

| 0,1,0,0                               | D3<br>D4       | 7                                            |        |          |     |              |         |    |          |                                        | Pag  | <b>10</b> 4 |     |             | 22<br>23       | 1        |          |         | -           | COM34<br>COM35          |

|                                       | D5             | 3                                            |        |          |     |              |         |    |          |                                        |      |             |     |             | 24<br>25       |          |          |         |             | COM36<br>COM37          |

|                                       | D7             | }-                                           | Н      | 4        | +   | _            | Н       |    | H        |                                        |      |             |     | <del></del> | 26<br>27<br>28 | 1/       | 32       |         |             | COM38<br>COM39<br>COM40 |

|                                       | D1<br>D2       | -                                            |        |          |     |              |         |    |          |                                        |      |             |     |             | 29<br>2A       |          |          |         | ı           | COM41<br>COM42          |

| 0,1,0,1                               | D3<br>D4<br>D5 | ╣                                            |        |          | ١   |              |         |    |          |                                        | Pag  | <b>o</b> 5  |     |             | 2B<br>2C       | ]        |          |         |             | COM43<br>COM44          |

|                                       | D8<br>D7       | 1                                            |        |          |     |              |         |    |          |                                        |      |             |     |             | 2D<br>2E       |          |          |         |             | COM45<br>COM46          |

| <del> </del>                          | D0             | #1                                           |        | 1        | 卞   | 1            |         |    | -        |                                        |      |             |     |             | 2F<br>30       | 1        |          |         |             | COM47<br>COM48          |

| 0,1,1,0                               | D2 D3          | 1                                            |        |          | l   |              |         |    |          |                                        | Pag  | n 6         |     |             | 31<br>32       |          |          |         |             | COM49<br>COM50          |

| 0,1,1,0                               | D4<br>D5       | ]                                            |        |          |     | I            | ı       |    |          |                                        |      | •           |     |             | 33<br>34<br>35 |          | İ        |         |             | COM51<br>COM52          |

| · · · · · · · · · · · · · · · · · · · | D6<br>D7       |                                              |        | 1        |     |              |         |    |          |                                        |      |             |     |             | 36<br>37       |          |          |         |             | COM53<br>COM54<br>COM55 |

|                                       | D0<br>D1       |                                              |        |          |     |              |         |    |          |                                        |      |             |     |             | 38<br>39       |          |          |         |             | COM56<br>COM57          |

| 0,1,1,1                               | D2<br>D3<br>D4 | <b>                                     </b> |        |          | •   |              |         |    |          |                                        | Page | 7           |     |             | 3A<br>3B       | <b> </b> | .        |         |             | COM58<br>COM59          |

|                                       | D5<br>D6       | 1                                            |        |          |     |              |         |    |          |                                        |      |             |     |             | 3C<br>3D       |          |          |         |             | COM60<br>COM61          |

| 1,0,0,0                               | D7<br>D0       | H                                            | +      | +        | +   | $\downarrow$ | +       | 4  | 4        |                                        | Page | _           |     |             | 3E<br>3F       |          |          | ٦       | ł           | COM62<br>COM63          |

| Column                                | 480            | 8                                            | 3 2    | 3 8      | 3 8 | į            | 3       | 3  | 2        |                                        |      | S           | 3 5 | ន្តន        |                |          | -        |         | (           | COMS                    |

| 84                                    | <u> 18:</u>    | 3                                            |        | 18       | 4   | ŀ            | 毕       | 1  | 8        |                                        |      |             | 38  | 28          | F              | age      | 8 is     | acce    | ssed        | during                  |

| .[                                    | 35             | 8                                            | 3 0    | 18       | βδ  | Ž            | 3 8     | 3  | õ        |                                        |      | 3           | N N | 0130        | 1              | /65 c    | r 1/;    | 33 du   | ty.         | •                       |

Figure 4

| A 3 | A 2 | A 1 | AO | Page | Address |

|-----|-----|-----|----|------|---------|

| 0   | 0   | 0   | 0  |      | 0       |

| 0   | 0   | 0   | 1  |      | 1       |

| 0   | 0   | 1   | 0  |      | 2       |

| 0   | 0   | 1   | 1  |      | 3       |

| 0   | 1 . | 0   | Ō  |      | 4       |

| 0   | 1   | Ö   | -1 |      | 5       |

| 0   | ī   | i   | ō  |      | 6       |

| 0   | ī   | i   | 1  |      | 7       |

| ì   | Ō   | Ō   | Ō  |      | 8       |

### (4) Set Column Address

Specifies column address of display RAM. Divide the column address into 4 higher bits and 4 lower bits. Set each of them succession. When the microprocessor repeats to access to the display RAM, the column address counter is incremented by lduring each access until address 132 is accessed. The page address is not changed during this time.

Higher bits

Lorer bits

| AO | E | R/W | D7 | D6 | D 5 | D4 | D3 | D2  | D1  | DO  |

|----|---|-----|----|----|-----|----|----|-----|-----|-----|

| 0  | 1 | 0   | 0  | 0  | 0   | 1  | A7 | A 6 | A 5 | A 4 |

| 0  | 1 | 0   | 0  | 0  | 0   | 0  | A3 | A2  | A1  | ΑO  |

| A 7 | A 6 | A 5 | A 4 | A 3 | A 2 | A 1 | AO | Column address |

|-----|-----|-----|-----|-----|-----|-----|----|----------------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0              |

| 1   | 0   | 0   | 0   | 0   | 0   | 1   | 1  | 131            |

#### (5) Read Status

| ΑO | E | R/W | D7   | D6  | D 5    | D4    | D3 | D2 | D1 | DO |  |

|----|---|-----|------|-----|--------|-------|----|----|----|----|--|

| 0  | 0 | 1   | BUSY | ADC | ON/OFF | RESET | 0  | 0  | 0  | 0  |  |

BUSY: When high, the LCM is busy due to intirnal operation or reset. Any command is rejected until BUSY goes low, The busy check is not required if enough time is provided for each cycle.

ADC: Indicates the relationship beween RAM column address and segment drivers. When low, the display is normal and column address "131-n" corresponds to segment drivern. When high, the display is reversed and column address ncorresponds to segment driver n.

ON/OFF: Indicates whether the display is on or off. When goes low, the display turns on. When goes high, the display turns off. This is the opposite of Display ON/OFF command.

RESET: Indicates the initialization is progress by RES signal or by Reset command. When low, the display is on. When high, the LCM is being reset.

(6) Write Display Data Writes 8-bit data in disply RAM. As the coclumn address is incremented by I automatically after each write, the microprocessor can continue to write data of multiple words.

| ΑO | E | R/W | D7 | D 6 | D 5 | D 4 | D 3  | D2          | D 1 | DO |

|----|---|-----|----|-----|-----|-----|------|-------------|-----|----|

| 1  | 1 | 0   |    |     | Wr  | ite | data | <del></del> |     |    |

(7) Read Display Data Reads 8-bit data from display RAM area specified by column address and page address. As the column address is incremented by I automatically after each write, the microprocessor can continue to read data of multiple words. A single dummy read is required immedeately after column address setup. Refer to the display RAM section of FUNCTIONAL DESCRIPTION for datails. Note

that no display data can be read via the serial interface.

| ΑO | E | R/W | D7 | D6 | D5 | D 4  | D3  | D2 | D 1      | DO |

|----|---|-----|----|----|----|------|-----|----|----------|----|

| 1  | 0 | 1   | •  |    | Re | ad d | ata | ·  | <b>-</b> |    |

(8) ADC Select

Changes the relationship between RAM column address and segment driver. The order of segment driver output pins can be reversed by software. This allows flexible IC layout during LCD module assembly. For details, refer to the column address section of Figure 4. When displya data is written or read, the column address is incremented by l as shown in Figure 4.

| ΑO | E | R/W | D7 | D6 | D 5 | D4 | D3 | D2 | D 1 | DO |

|----|---|-----|----|----|-----|----|----|----|-----|----|

| 0  | 1 | 0   | 1  | 0  | 1   | 0  | 0  | 0  | 0   | D  |

When D is low, the right rotation (normal direction). When D is high, the left rotation (reverse direction). Fig.5 shows the status.

| LCD o | utput | 00      |                | 00131    |

|-------|-------|---------|----------------|----------|

| ADC   | "0"   | 0(H) →  | COLUMN ADDRESS | → 83 (H) |

| (DO)  | "1"   | 83(H) ← |                | ← 0 (H)  |

(9) Nomal/reverse Display Reverses the Display ON/OFFstatus without rewriting the contents of the display data RAM.

|   | ΑO | E | R/W | D7 | D 6 | D 5 | D 4 | D3 | D2 | D1 | DO |  |

|---|----|---|-----|----|-----|-----|-----|----|----|----|----|--|

| l | 0  | 1 |     | 1  |     |     |     |    |    |    | L  |  |

When D is low, the RAM data is high, being LCD ON potential ( normal display).

When D is high, the RAM data is low, being LCD ON potential. ( reverse display).

(10) Entire Display ON

Forcibly turns the entire display on regardless of the contents of the display data RAM. At this time, the contents of the display data RAM are held,

This command has priority over the Normal/Reverse Display command. When D is low the normal display status is provided.

| AO | E | R/W | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |

|----|---|-----|----|----|----|----|----|----|----|----|

| 0  | 1 | 0   | 1  | 0  | 1  | 0  | 0  | 1  | 0  | D  |

When D is high, the entire display ON status is provided. If the Entire Display ON command is executed in the display OFF status, the LCD panel enters Power Save mode. Refer to the Power Save section for details. (11) Set LCD Bias

Selects a bias ratio of the voltage required for driving the LCD. This command is enabled when the voltage follower in the power supply circuit operates.

| A | E | R/W | D7 | <b>D</b> 6 | D5 | D4 | D3 | D2 | D1 | DO |

|---|---|-----|----|------------|----|----|----|----|----|----|

| 0 | 1 | 0   | 1  | 0          | 1  | 0  | 0  | 0  | 1  | D  |

| D | Bias ratio of LCD power supply |

|---|--------------------------------|

| 0 | 1/8 bias<br>1/6 bias           |

(12) Read-Modify-Write

A pair of Read-Modify-Write and End commands must always be used. Once Read-Modify-Write is issued. column address is not incremented by Read Display Data command but incremented by Write Display Data command only. It continues until End command is issued. When the End is issued.column address returns to the address when Read-Modify-Write was issued. This can reduce the microprocessor load when data of a specific display area is repeatedly changed during cursor blinking or others.

| AO | E | R/W | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |

|----|---|-----|----|----|----|----|----|----|----|----|

| 0  | 1 | 0   | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 0  |

Note: Any command except Read/Write Display Data and Set Column Address can be issued during Read-Modify-Write.

(13) End

Cancels Read-Modify-Write mode and returns coumn address to the original address (when Read-Modify-Write was issued).

| AO | E | R/W | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |

|----|---|-----|----|----|----|----|----|----|----|----|

| 0  | 1 | 0   | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 0  |

(14) Reset

Resets the Initial Display Line register. Column Address counter. Page Address register, and output status selector circuit to their initial status. The Reset command does not affect on the contents of display RAM. Refer to the Reset circuit section of FUNCTIONAL DESCRIPTION.

| AO | E | R/W | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |  |

|----|---|-----|----|----|----|----|----|----|----|----|--|

| 0  | 1 | . 0 | 1  | 1  | 1  | 0  | 0  | 0  | 1  | 0  |  |

The Reset command cannot initialize LCD power supply. Only the Reset signal to the RES pin can initialize supplies.

(15) Set Power Control

Selects one of eight power circuit funcitions using 3-bit register. An extemal power supply and part of intemal power supply functions can be used simultaneously. Refer to Power Circuit section of FUNCTIONAL DESCRIPTION for details.

| AO | E | R/W | D7 | D6 | D5 | D4 | D3 | D2 | D1  | DO |  |

|----|---|-----|----|----|----|----|----|----|-----|----|--|

| 0  | 1 | 0   | 0  | 0  | 1  | 0  | 1  | A2 | A1' | AO |  |

When AO goes low.voltage follower turns off. When AO goes high it turns on.

When Al goes low.voltage regulator turns off. When Al goes high it tuons on.

When A2 goes low.voltage booster turns off. When A2 goes high it turns on.

turns on.

(16)Set Electronic Control

Adjusts the contrast of LCD panel display by changing V5 LCD drive voltage that is output by voltage regulator of on-board power supply.

This command selects one of 32 LCD drive voltages by storing data in 5-bit register. The voltage adjusing range should be determined depending on the external resistance. Refer to the Voltage Regulator Circuit section of FUNCTIONAL DESCRIPTION for details.

| AO | E | R/W | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |  |

|----|---|-----|----|----|----|----|----|----|----|----|--|

| 0  | 1 | 0   | 1  | 0  | 0  | A4 | А3 | A2 | A1 | AO |  |

| D4          | D3          | D2    | D1          | DO ·        | Driving Voltage |

|-------------|-------------|-------|-------------|-------------|-----------------|

| 0 0         | 0           | 0     | 0<br>0<br>1 | 0<br>1<br>0 | Low             |

| 1<br>1<br>1 | 1<br>1<br>1 | 1 1 1 | 0<br>1<br>1 | 1<br>0<br>1 | ↓<br>High       |

Set register to (D4.D3.D2.D1.D0) = (0.0.0.0.0) to suppresselectronic control function.

(17) Static Indicator

This command turns on or off static drive indicators. The indicators display is controlled by this command only, and it is not affected by the other display control commands. Either FR or FRS terminal is connected to either of static indicator LCD drive electrodes and the remaining terminal is connected to another electrode. When the indicator is turned on the static drive operates and the indication blinks at an interval of approximately one second. The pattern separation between indicator electrodes are dynamic drive electrodes is recommended. A closer pattern may cause an LCD and electrode deterion at ion.

| AO | E | R/W | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |

|----|---|-----|----|----|----|----|----|----|----|----|

| 0  | 1 | 0   | 1  | 0  | 1  | 0  | 1  | 1  | 0  | D  |

D 0:Static indicator OFF 1:Static indicator ON

(18) Power Save (Compound Command)

When all displays are turned on during indicator off the Power Save command is issued to greatly reduce the crrrent consumption.

IF the static indicators are off, the Power Sare command sleeps the system. If on, this command stands by the system.

Static OFF

Indicator ON

Power Save (compound command)

(Sleep mode)

Sleep mode

(Standby mode)

This mode stops every operation of the LCD display system.and can reduce current consumption nearly to a static current value if no access is made from the microprocessor. The internal status in the sleep mode is as follows:

(1) Stops the oscillator circuit and LCD power supply circuit.

(2) Stops the LCD drive and outputs the VDD level as the segment/common driver output.

(3) Holds the display data and operation mode proviede before the start of hte sleep mode.

(4) The MPU can access to the built-in display RAM.

Standby mode Stops the operation of the duty LCD display system and truns on only the static drive system to reduce current consumption to the minimum level required for static drive.

The ON operation of the static drive systim indicates that the LCM

is in the standby mode. The internal status in the stanby mode is as

follows:

(1) Stops the LCD power supply circuit.

(2) Stops the LCD drive and outputs the VDD level as the segment/common driver output. However, the intermal staic drive system operates.

(3) Hold the display data and operation mode provided before the st-.

art of the standby mode.

(4) The MPU can access to the built-in display RAM. When the RESET command is issued in the standby mode, the sleep mode is set.

When the LCD drive voltage level is given by an external resistive driver, the current of this resistor must be cut so that it may be fixed to floating or VDD level, prior to or concurently with causing the LCM to go to the sleep mode or stanby mode.

When an external power supply is used likewise the function of this external power supplay must be stopped so that it may be fixed to floating or VDD level, prior to ro concurrently with causing the LCM to go the sleep mode or stanby mode.